GRVI Phalanx implements a thousand core processor

About GRVI Phalanx, a massively parallel RISC-V FPGA accelerator, a combination of GRVI and Phalanx. GRVI is an FPGA-implemented RISC-V RV32I soft processor core, and is also a parallel processor with the best performance/area for handcraft mapping and processing elements. GRVI implements a single-stage pipeline of 2 or 3 levels, consuming 320 6-LUTs in a Xilinx UltraScale FPGA board, and is currently optimally placed and optimized in the embedded BRAM of a Kintex UltraScale(-2) board. The maximum operating frequency during configuration can reach 300-375MHz. Phalanx is a massively parallel FPGA accelerator framework designed to reduce the effort and effort required to develop and manage FPGA accelerators. In addition, Phalanx is a mixture of a large number of soft core clusters and accelerator cores that provide additional storage and I/O interfaces in an on-chip network with Hoplite routing. Detailed information on GRVI Phalanx can be found in a paper entitled "GRVI Phalanx: A Massively Parallel Risc-V FPGA Accelerator Accelerator" published at the IEEE 24th International FCCM Symposium 2016.

1680 open source ISA RISC-V processor cores run on Virtex UltraScale+ VU 9P FPGAs:

Blogger Jan Gray recently published a blog about the Chi-Core RISCV processor, which mentions that it is now possible to run 1680 open-source concurrently on the Xilinx Virtex UltraScale+ VU9P (which is a medium-sized Virtex UltraScale+ FPGA board) board. The RISC-V processor core and successfully tested the GRVI Phalanx massively parallel accelerator framework. According to the blogger, this is the first application of the first-generation nucleus RISC-V to run successfully, and it is also the application that runs the largest number of 32-bit RISCV cores on a single chip regardless of the technology used.

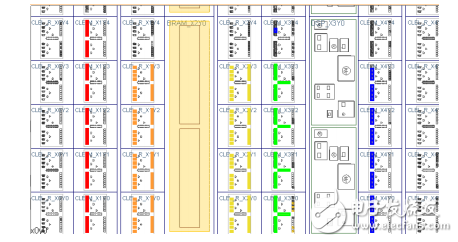

Below is a scene diagram of the 1680 RISCV cores running on the FPGA board:

This 1680 core GRVI Phalanx is not only the first operational Megacore RISC-V, but also the first 1000-bit RISC core running on the FPGA. It can also run 32-bit RISC on a single chip. The combination with the largest number of cores.

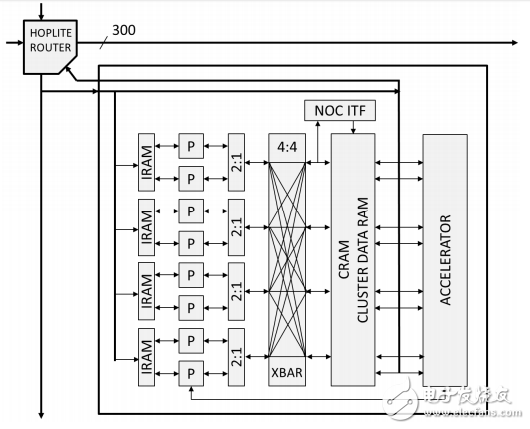

The GRVI Phalanx design consists of 210 processor clusters, each containing eight open source RISC-V processor cores, 128KB of multiport RAM, and a 300-bit Hoplite NOC route. The following figure is a block diagram of a Phalanx cluster:

However, it should be noted that although the RISC-V reduced instruction set is open source and there are a large number of open source implementations based on the RISC-V instruction set on its official website, the GRVI Phalanx acceleration framework is not open source.

to sum up:

The concept of the thousand-core processor was first proposed by IBM, and IBM also developed a low-power, high-performance microprocessor with 1025 cores. It can be seen that in the pursuit of the single-core running speed to the extreme, multi-core, even thousands of core parallel computing has emerged, and a single-core 32-bit multi-core processor can be successfully run on a single FPGA chip, which is enough to see Xilinx FPGA. The ability can not be underestimated.

Silicon TVS / TSS:

Diode TVS (Transient Voltage Suppressor), also known as Transient suppression diodes, is widely used a new type of high efficient circuit protection device, it has a fast response time (the nanosecond) and high surge absorbing ability.When it ends of stand moments of high energy shock, TVS can bring the two ends at high rate from high impedance to a low impedance between impedance values, to absorb a large current moment, put it at both ends of the voltage restraint on a predetermined value, thus protecting the back of the circuit components are not affected by the impact of the transient high pressure spikes.

Silicon TVS Transient Voltage Suppresso,Silicon TSS Transient Voltage Suppresso

YANGZHOU POSITIONING TECH CO., LTD. , https://www.yzpst.com