Realization of low phase noise high purity spectrum digital frequency converter

Abstract: The design of an X-band frequency synthesizer, and this program will direct digital lock combination, rapid completion agility feature.

introduction

Modern radars are increasingly demanding frequency synthesizers for phase noise, fast agility, flexible waveform generation, and in-band spurs. The full-coherent direct frequency synthesizer has high frequency stability and short frequency hopping time. The shortcoming of the direct frequency synthesizer is spurious suppression, and the amount of equipment is huge. A disadvantage of the phase-locked frequency synthesizer is that if the total frequency division ratio of the loop is too large, the phase noise of the output is seriously deteriorated; and the frequency conversion speed is slow. Therefore, the direct multiplier and digital lock are combined, and the design of the scheme is completed by using the fast switching speed of the switch, the frequency stability of the direct multiplier, and the flexibility of the digital phase lock.

System Block Diagram

Figure 1 is a block diagram of the X -band frequency synthesizer.

When the digital phase-locked loop works intermittently (the digital phase-locked loop is only used for frequency capture ) , the digital phase-locked loop lock time takes 40~50ms . This is because the loop filter output voltage is always saturated during the stop of the digital phase-locked loop. When the digital phase-locked loop is re-working, it must go through a long recovery time to work properly. The frequency capture time of the digital phase-locked loop is too short, but its digital interface is flexible and variable. One ring can fulfill the requirements of multiple stable frequency points, and the corresponding equipment is small. The speed of the electronic switch is nS , which can meet the needs of rapid agility. With a little design during frequency control, the advantages of both can be effectively combined. When the switch is selected from the first ring to the second ring, the second ring is stable on the previous clock, and the agility time is determined by the switch; meanwhile, the first ring is controlled by the digital interface to change the frequency. And so on, when the next clock is selected, when the switch is selected by the second ring to the first ring, the first ring is stable on the previous clock, and the agility time is determined by the switch. Therefore, the difficulty of direct frequency multiplication - spurious suppression is well solved. Â Â Â Â

The frequency band is then broadened by the frequency multiplier.

The X -band upconverter is the main source of spurious signals. Because it is broadband mixing, there will be intermodulation components in the passband. Two measures are taken here. One measure is to calculate the input signal of the mixer (fi ) and input the local oscillator signal (fL) so that mfL ± nfi ( except fL+fi ) falls within the band as little as possible. Another measure is to use the switching filter component after the mixer, divide the wideband filter into several narrow filters, and select the corresponding filter to effectively suppress the intermodulation component.

Figure 1 Â Frequency synthesizer block diagram

Figure 2 Â Â Digital phase lock principle block diagram

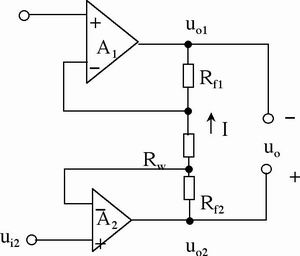

Figure 3 Â In-phase parallel differential amplifier

Design Points

Digital phase-locked frequency synthesizer

For a phase-locked synthesizer with a high operating frequency and a relatively small frequency conversion interval, if the pre-frequency division method is used, the loop frequency division is relatively large. Frequency shifting in the feedback branch can effectively reduce the loop division ratio, which is beneficial to improve the phase noise and dynamic corresponding characteristics of the system. This is a commonly used lock-in synthesizer. The working principle is that the reference signal and the feedback signal are phase-compared in the PD , the output voltage is controlled by the loop filter LPF to suppress the noise and the high-frequency component to control the VCO , and the system realizes the frequency conversion by controlling the frequency division ratio after the frequency shift of the feedback branch. When the loop is locked, the output frequency is f0=(m+N/p)fi . Its block diagram is shown in Figure 2 .

Loop gain selection: When selecting the loop bandwidth, the loop bandwidth is much smaller than the loop gain, so at the time of design, adding a first-order amplifier between the phase discriminator / phase detector and the loop filter is greatly Increased loop gain ensures improved phase noise metrics. The amplifier circuit is shown in Figure 3 .

Because the structure of the in-phase parallel differential amplifier circuit is symmetrical, the external circuit with symmetric parameters should be selected, that is, Rf1=Rf2=Rf . At this time, the differential mode gain is:

It can be concluded from the above equation that the in-phase parallel differential amplifier can adjust the gain conveniently only by changing the Rw size. The external circuit does not need a matching resistor, and the output can obtain a very high common mode rejection ratio.

The choice of loop bandwidth: the power of the phase noise of the voltage controlled oscillator is mainly concentrated in the low frequency part, and the high frequency filtering effect of the error transfer function of the phase locked loop is quite remarkable. At the low end of F < fn , the amount of attenuation rises by 20 dB every 10 octaves . From the above analysis, only from the filter voltage controlled oscillator noise, the larger the fn , the better.

However, the crystal noise as the reference oscillator acts on the input of the loop phase detector. The loop filters the crystal noise low. The filtering depends on the frequency response of the closed-loop transfer function. In the high frequency range of F < fn , Decrease by -10dB every 10 octaves . From the above analysis, only the filter input crystal phase noise is smaller , and the smaller the fn of the loop, the better.

In the same coordinate system, the phase noise spectrum of the VCO is first made , and then the N2 multiplied crystal phase noise spectrum is obtained. The intersection of the two spectral lines can be found, as long as the fn of the loop is selected at the intersection frequency, the output phase The noise power is minimal. As long as all the noise is merged into two types, high-pass type and low-pass type, the same method can be used to complete the design of the best fn .

The loop filter uses an active proportional-integral filter with characteristics close to the ideal integral filter. It has two independently adjustable parameters and has a hysteresis - lead characteristic, which is beneficial to the stability of the loop.

Based on the DDS chirp signal source

DDS is mainly composed of phase accumulator, sin amplitude converter, D/A converter and low-pass filter (LPF) . The core component is phase accumulator, as shown in Figure 4 , under the action of system clock, The phase accumulator completes the frequency accumulation, and each time the accumulated result is used as a sampling address, periodically scans the waveform memory of the sine wave, and converts the result into a voltage waveform through a D/A converter.

The relationship between the output frequency, the frequency control word, and the system clock frequency is:

Where: FO —the frequency of the output waveform; K —the frequency control word;

FCLK — system clock frequency; N — phase accumulator bit length.

In addition to the main spectrum, the DDS synthesized signal has a large number of spurious components. These spurious components mainly have three sources, one is caused by the phase truncation error, which can be used to address the phase / amplitude after the phase accumulator output phase is truncated. The number of bits in the conversion table is measured. Second, the number of bits of the waveform memory ROM is limited, causing the waveform amplitude quantization error, which is determined by the number of bits of the output digital and the number of DACs after the phase / amplitude conversion, and the third is due to the DAC . Non-ideal characteristics, the staircase wave produces harmonic and spurious components at the DAC output. In this system, the DDS chip uses ADI 's AD9854 as its core, the spur caused by phase truncation is negligible, and the quantization error can be based on the actual waveform bandwidth, using oversampling technology plus filtering to obtain a higher signal-to-noise ratio. The non-ideal characteristics of the DAC , in practical use, only a DAC with good linearity can be selected to improve the quality of the DDS output signal.

Experimental result

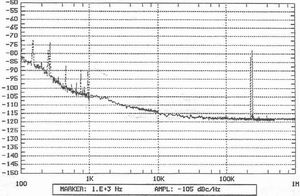

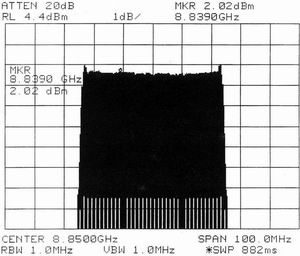

According to the block diagram shown in Figure 1 , the X -band frequency synthesizer's local oscillator sideband phase noise power spectral density curve (fo=9500MHz) is shown in Figure 5. The transmission path bandwidth is 50MHz. The chirp signal waveform is shown in Figure 6 . .

Figure 4 Â DDS function block diagram

Figure 5 Â Single sideband phase noise power spectral density curve

Figure 6 Â 50MHz chirp signal waveform

Conclusion

Digital integrated phase-locked loop has become the core of indirect frequency synthesizer because of its easy debugging, small size and low power consumption. DDS is widely used due to its wide bandwidth, programmable and fully digital structure, through analysis and system. In the verification, the program has a satisfactory effect.

HDI PCB Specification

High density interconnect (HDI) PCBs represent one of the fastest-growing segments of the printed circuit board market. Because of its higher circuitry density, the HDI PCB design is able to incorporate finer lines and spaces, smaller vias and capture pads, and higher connection pad densities. A high density PCB features blind and buried vias and often contains microvias that are .006 in diameter or even less.

HDI PCBs are characterized by high-density attributes including laser microvias, fine lines and high performance thin materials. This increased density enables more functions per unit area. Higher technology HDI PCBs have multiple layers of copper filled stacked microvias (Advanced HDI PCBs) which creates a structure that enables even more complex interconnections. These very complex structures provide the necessary routing solutions for today's large pin-count chips utilized in mobile devices and other high technology products.

The HDI PCBs we offer include the following highly requested characteristics:

Blind and/or buried vias

Via-in-pad

Through vias from surface to surface

20 µm circuit geometries

30 µm dielectric layers

50 µm laser vias

125 µm bump pitch processing

Applications

HDI PCB is used to reduce size and weight, as well as to enhance electrical performance of the device. HDI PCB is the best alternative to high layer-count and expensive standard laminate or sequentially laminated boards. HDI incorporate blind and buried vias that help to save PCB real estate by allowing features and lines to be designed above or below them without making a connection. Many of today's fine pitch BGA and flip-chip component footprints do not allow for running traces between the BGA pads. Blind and buried vias will only connect layers requiring connections in that area.

HDI PCB

HDI PCB,Special HDI PCB,HDI Prototype PCB,HDI Board PCB

Storm Circuit Technology Ltd , http://www.stormpcb.com