Wireless Applications: OS Selective Considerations for All-Programmable SoCs

Gu Yuan, Senior Manager, Xilinx Communications Division

With the explosive growth of wireless data throughput, digital signal processing technology and radio equipment are under tremendous pressure to improve. The current focus is on 4G LTE. 4G networks are being deployed on a large scale throughout the world. And now we have seen early development work on 5G networks. The goal is to increase data capacity by a factor of 1000 on the basis of 4G networks. This emerging technological development has raised new requirements for system manufacturers to constantly evolve—they must increase system integration and system performance, reduce system bill of materials (BOM) costs, increase design flexibility, and speed time to market.

Although the hardware solutions supported by traditional ASIC devices can achieve power and cost targets, the NRE is extremely high, the flexibility is poor, and the product launch process is very slow. To meet these requirements and meet these challenges, Xilinx introduced the All Programmable SoC (APSoC) architecture to the industry and successfully implemented it in the Zynq-7000 product family.

The Zynq-7000 device uses the Xilinx APSoC architecture with hardware, software, and I/O reprogrammability to enable greater system-level differentiation, higher levels of integration, and flexibility (Figure 1). Since its introduction in December 2011, the Zynq-7000 device has been widely used in many markets including communications, data center, automotive, industrial, aerospace and defense. For the communications market (especially for wireless applications), the Zynq-7000 brings unique advantages: its integrated programmable logic (PL) is specifically optimized for digital signal processing; its ARM Cortex A9 processing subsystem ( PS) can effectively implement the control functions of typical wireless devices such as remote radio units and wireless backhaul units.

Figure 1: Zynq-7000 All Programmable SoC Architecture

When building a wireless application based on the Zynq APSoC device, you must choose an operating system that meets the application requirements. For this reason, several key factors need to be considered for different wireless applications:

1. Carrier-class operational capabilities: For carrier-class systems, the system reliability is generally required to reach 99.999%. The reliability of the unit must reach this high during normal working hours. From an operational point of view, it represents the support of various features of the system, such as cold/hot start, fault monitoring, detection and processing, and redundancy.

Real-time processing: Real-time means predictable response times, not just "very fast." Remote radio units have different real-time requirements compared to wireless backhaul processing. The signal processing tasks of radio equipment are heavy, and the processor used to support signal processing must meet strict timing budget requirements.

3. Diagnosis: In order to support on-site diagnosis and post-mortem diagnosis, it is necessary to collect and store a large amount of performance measurement data and log data. Therefore, it should have the ability to track and manage some of the key indicators important for wireless applications, such as performance measurement and statistical indicators, CPU utilization and fault monitoring indicators, OS task switching indicators and event history indicators.

4. Tools and protocol integration: Full integration of debugging and diagnostics environments, plus some specific network protocol stacks provided by some OS vendors, help designers to develop and maintain effective systems.

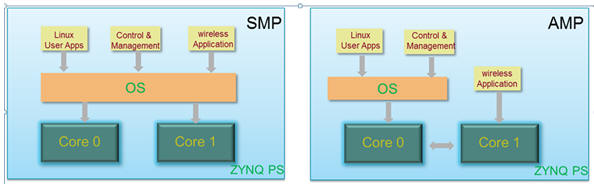

The Zynq SoC integrates two ARM Cortex A9 cores. Software architects need to choose between two currently supported multiprocessor architectures: SMP (Symmetric Multiprocessing) or AMP (Asymmetric Multiprocessing). As shown in Figure 2, in an SMP system architecture, two or more identical processors share resources and run an OS instance. In theory, this architecture will treat all processors equally under the same OS instance. In contrast, the AMP architecture treats each processor differently, regardless of whether there is an OS instance or not, and the processors are also isolated from each other. A kernel that is not running an OS may be running microcode that is considered a "bare metal" instance.

In general, SMP provides a unified OS platform for higher-level applications. Software architects do not need to consider resource sharing and inter-process communication between two cores when building applications on the OS. In addition, there are performance overheads for SMP, which can adversely affect the performance of time-critical wireless applications. Comparing SMP and AMP, AMP software is simplified in the case of operating an OS instance. Basically, there is no overhead at all, but it requires careful software design to achieve processor resource sharing and interprocessor communication.

Figure 2: Comparison of SMP and AMP

Using Zynq APSoC devices can be very efficient to achieve a variety of key wireless applications, including radio frequency and wireless backhaul. Each wireless application has different performance requirements and requires the OS to support different features. RF applications are a good example of Zynq's fully integrated hardware and software solutions for implementing all digital front ends and processing functions.

The RF digital front-end application is a major component of a typical remote radio unit (RRH) in a 4G network. The application's processing requirements can be divided into signal processing and control processing. In the field of signal processing, Zynq can be used to implement high sample rate filters, crest factor suppression (CFR), and digital predistortion (DPD) for digital upconversion/downconversion. DPD is a special case. It needs to use Zynq's PS and PL at the same time.

DPD processing can be subdivided into high-speed data paths and update paths. The update path is used to periodically update the coefficients of the filter bank and is well suited for implementation in the ARM Cortex A9 core. In general, the coefficient update must be completed in milliseconds to tens of milliseconds. Due to the computational complexity of arithmetic, the A9 core and the embedded NEON SIMD vector computing unit can be combined to meet the required high performance. In addition, the Zynq PL also supports hardware acceleration for processor clock cycle-intensive functions so that the Zynq PL, ARM A9 core, and NEON coprocessors can be used together.

The control processing side of the radio is typically used for initial radio calibration, configuration, alerting, scheduling, and network messaging. This does not generally require high performance in radio applications, so it is easy to manage using an ARM A9 core in Zynq.

Choosing the right architecture to support DPD application and control processing applications is important because it determines overall performance, reliability, and ease of maintenance.

The common architecture chosen for wireless RF applications is the AMP mode. In this mode, a complete ARM core runs in a bare-metal mode, dedicated to DPD processing, providing greater computational margins for meeting the time requirements for updating DPD coefficients. Other applications such as control and OAM run on the second ARM A9 core controlled by the OS. In this architecture, since the OS controls only one of the two ARM cores, an interprocessor channel must be established between applications running on two separate cores, such as using OCM (on-chip memory) or shared memory. This approach is important for certain critical control applications, such as those used to monitor the health of DPD modules. This inter-process communication (IPC) solution is non-standard and must be developed separately in the AMP mode.

The SMP architecture is very simple and intuitive, using a single OS instance to simultaneously control two ARM cores and control all applications. IPC, debugging, and support tool chains are all in the same OS. To ensure that resources are used exclusively for DPD applications, special techniques such as "Core Affinity" and "Interrupt Masking" can be used in software applications. In the previous case, the DPD application will only run on one core, that is, no other tasks share resources (except OS scheduler overhead). In the latter case, the interrupt service (except triggered by the DPD application) is transferred to run on the second core. This resource is fully utilized by the DPD application.

So Zynq APSoC is the ideal platform to support AMP or SMP architecture. As shown in Figure 3, Zynq integrates dual-core ARM processor, 12.5Gb/s serial transceiver (SerDes), higher reliability 500MHz+ DSP, and can provide complete digital front-end functions such as DPD, CFR, DUC /DDC and CPRI/JESD interfaces. This solution eliminates the need to provide an interface between the processor and the individual FPGAs, simplifying the PCB design.

The single-chip integrated solution migrated from the discrete multi-chip solution to the Zynq platform is very simple and intuitive. Xilinx provides comprehensive and comprehensive hardware and software solutions that will facilitate the successful migration to Zynq. This includes digital signal processing IP libraries for DUC, DDC, CFR, and DPD. In addition, a variety of OS solutions are supported, including device drivers, boot loaders, BSP templates, and common tools. After a successful migration to the Zynq platform, the solution can significantly increase system performance, save overall power consumption, and reduce bill of materials (BOM) costs.

Figure 3: Migrating from a discrete solution to a Zynq solution

In this article, we discussed the main factors that should be considered when selecting operating systems for wireless applications, the architecture and considerations for wireless applications (AMP vs. SMP), and the direct application of the above mentioned Xilinx 7000 devices. In summary, Xilinx offers advanced devices of this kind that can help wireless network infrastructure designers improve the performance of the software and hardware while achieving full programmability, improve system integration, and reduce BOM and total system cost. Consumes, achieves high reliability and accelerates the time to market. Designers can now not only develop devices faster, but they can also continue to provide field updates long after the device is deployed, thereby avoiding the risks associated with devices such as ASSPs and ASICs.

mask

Dongguan Formal Precision Metal Parts Co,. Ltd , https://www.formalmetal.com